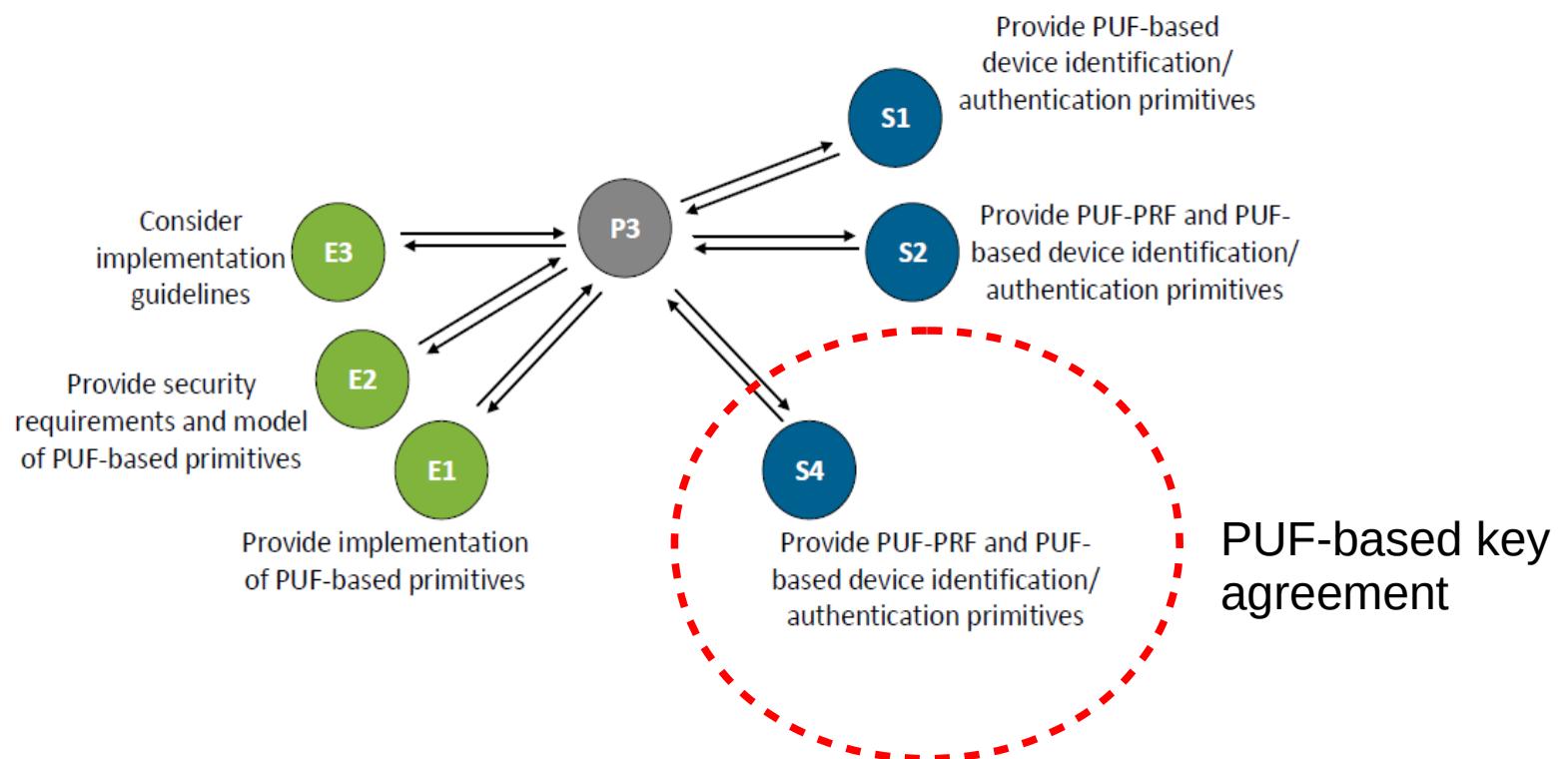

# P3 – Hardware-entangled cryptography

Cryptography based on hardware characteristics

# Who we are

Stefan Katzenbeisser

Ahmad-Reza Sadeghi

André Schaller

Nikolaos Athanasios

Anagnostopoulos

Ghada Dessouky

# Motivational use cases

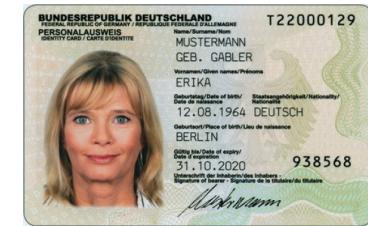

- Authentication and identification

- Integrity of devices

- Anti-counterfeiting

- Tamper-evidence

- Lightweight security

# Hardware-entangled cryptography

## Physical(ly) Unclonable Functions (PUFs)

- Functions embedded into physical objects

- Manufacturing process variations

→ unique identity for ICs

- Primitives similar to those employed in biometrics

- “Hardware biometrics”

Stefan Katzenbeisser

André Schaller

Nikolaos Athanasios Anagnostopoulos

# Principles of PUFs

## Physical(ly) Unclonable Functions (PUFs)

- Functions embedded into physical objects

- Manufacturing process variations

→ unique identity for ICs

- When queried with a challenge, a PUF generates a response (Challenge-Response Pair; CRP)

- The response depends on

- the challenge **and**

- specific physical properties of the object

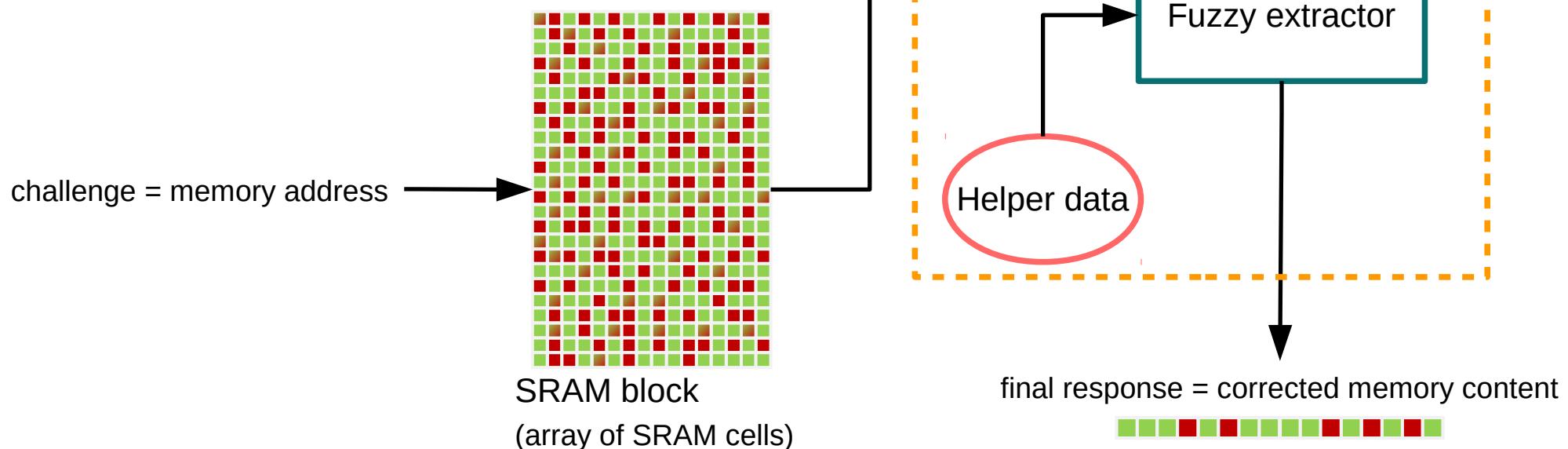

# Principles of PUFs

## Error correction mechanism

- Fuzzy extractor

- Helper data, based on registration

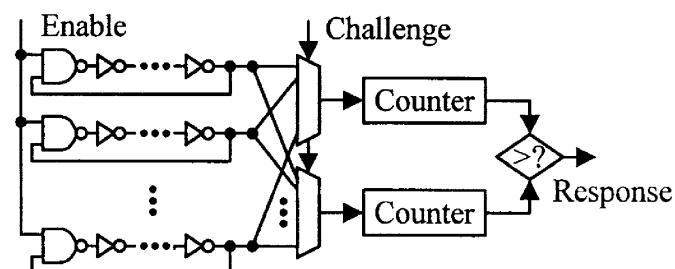

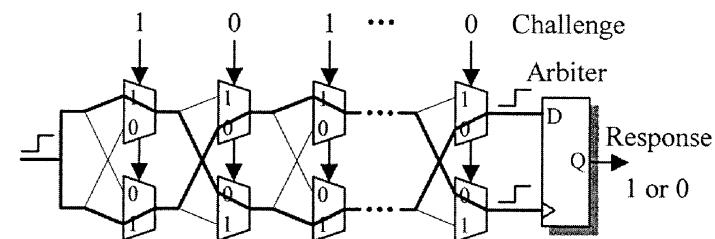

# Strong and weak PUFs

## Strong PUFs

- Multiple challenge-response pairs

- Delay-based PUFs

- Still on the prototype stage

# Strong and weak PUFs

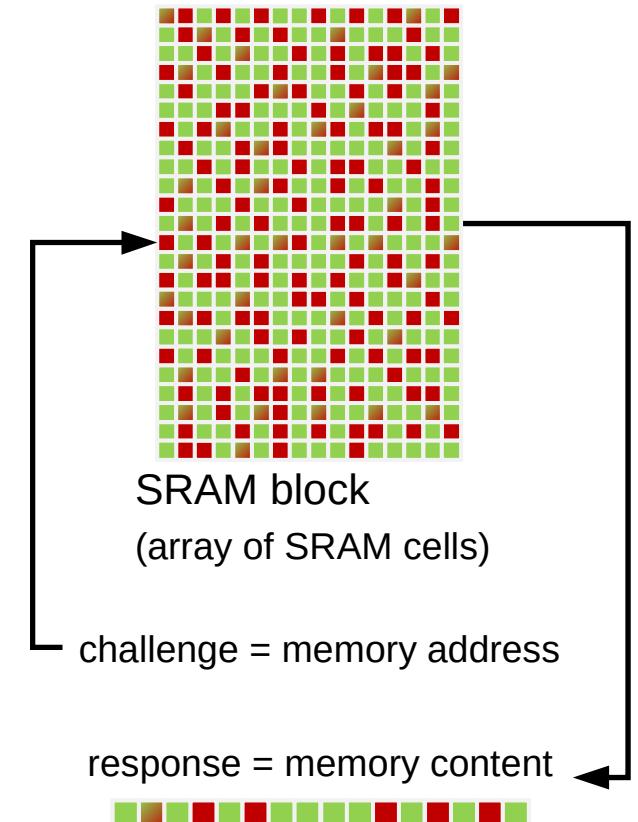

## Weak PUFs

- A single or very few challenge-response pairs

- Memory-based PUFs

- In production stage

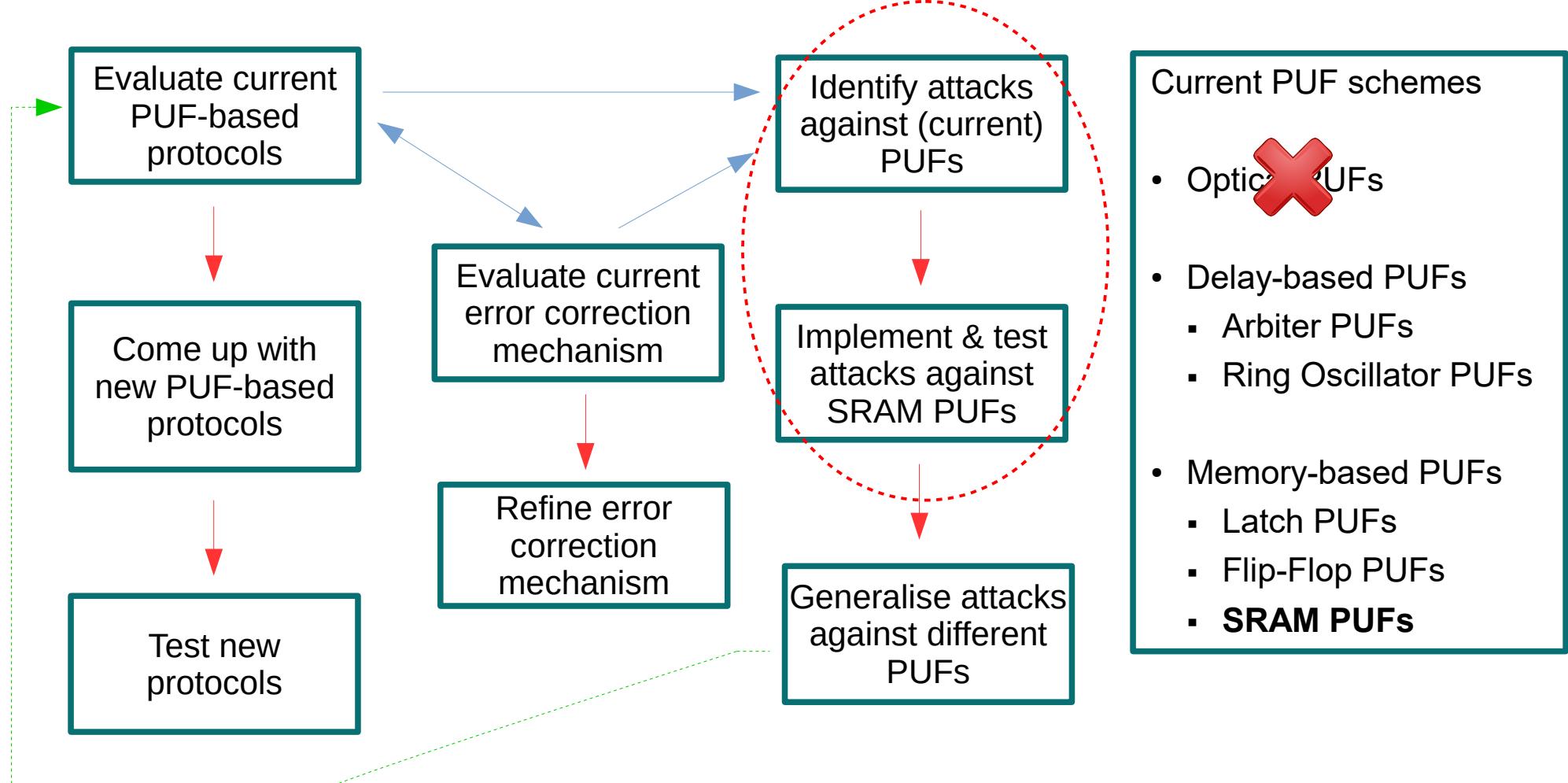

# What we do

# Attacks on PUFs

## Desired effect

- Get/Predict/Model challenge-response pair

- Man in the middle

- Physical access

- Logical access

- Disable/Make unavailable/Break PUF

- Destroy PUF

- Bypass PUF

- Force PUF into producing specific result

- Physical access

- Logical access

# Attacks on PUFs

## Means and ways of attacks

- Hardware

- Side-channel

- Invasive

- Software

- Internal

- External

- Man in the middle

- Cloning (Guessing + error correction)

- Target

- PUF structure itself

- Error-correction mechanism

# Attacks on PUFs

## Reasons

- Availability

- Integrity

- Confidentiality

## Attacks as a means of protection

- Deniability

- Denial of access for third parties

- PUF as a single (unique) point of failure

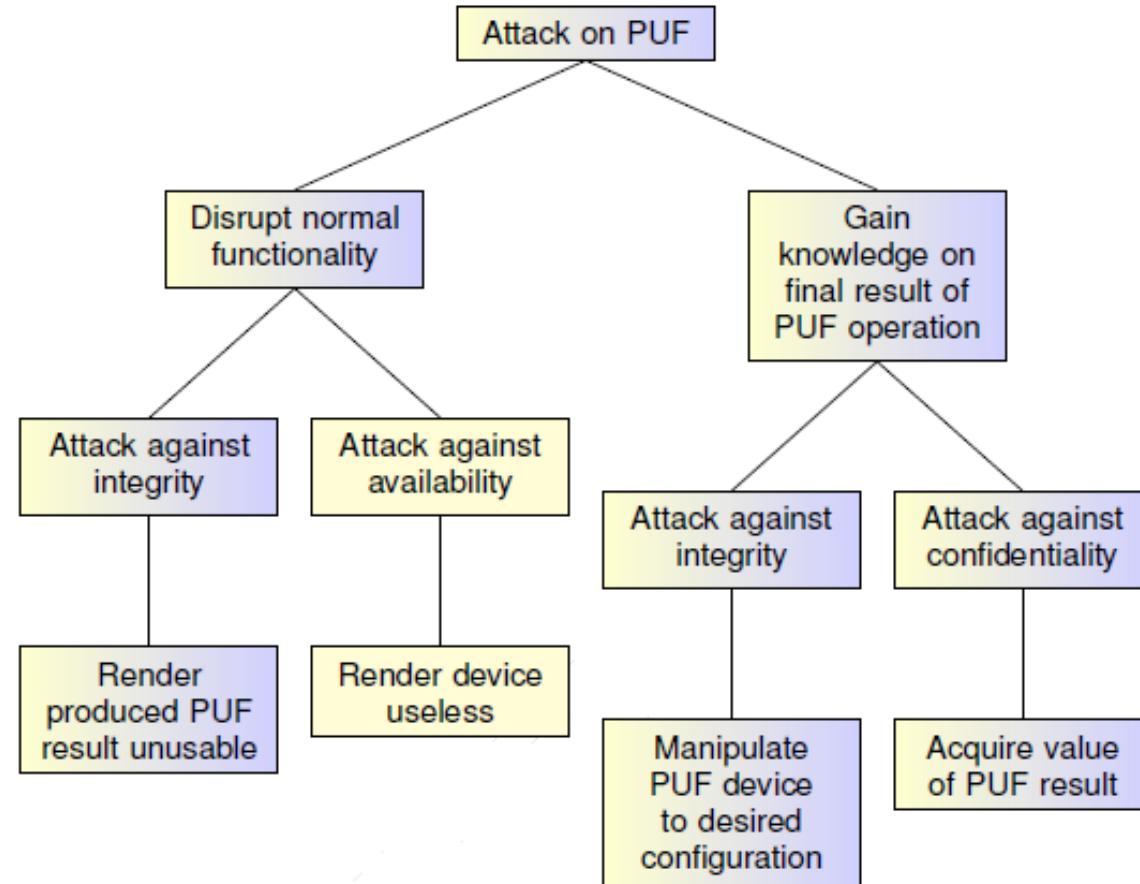

# Classification of attacks in the form of an attack tree

# Classification of attacks in the form of an attack tree

## Advantages

- Classification according to previous criteria

- Means of calculating cost and appropriateness

- Thus, also, a way to identify possible vulnerabilities and assess security

- Can lead to an estimation of *acceptable* risk and thus to assessment of PUFs as security mechanisms

# Implementation and testing of attacks

- Work in progress

- Selected attacks are being implemented against SRAM PUFs

- Aging

- Data remanence

- Manipulation of neighbouring cells

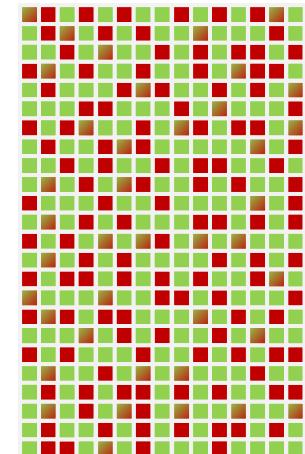

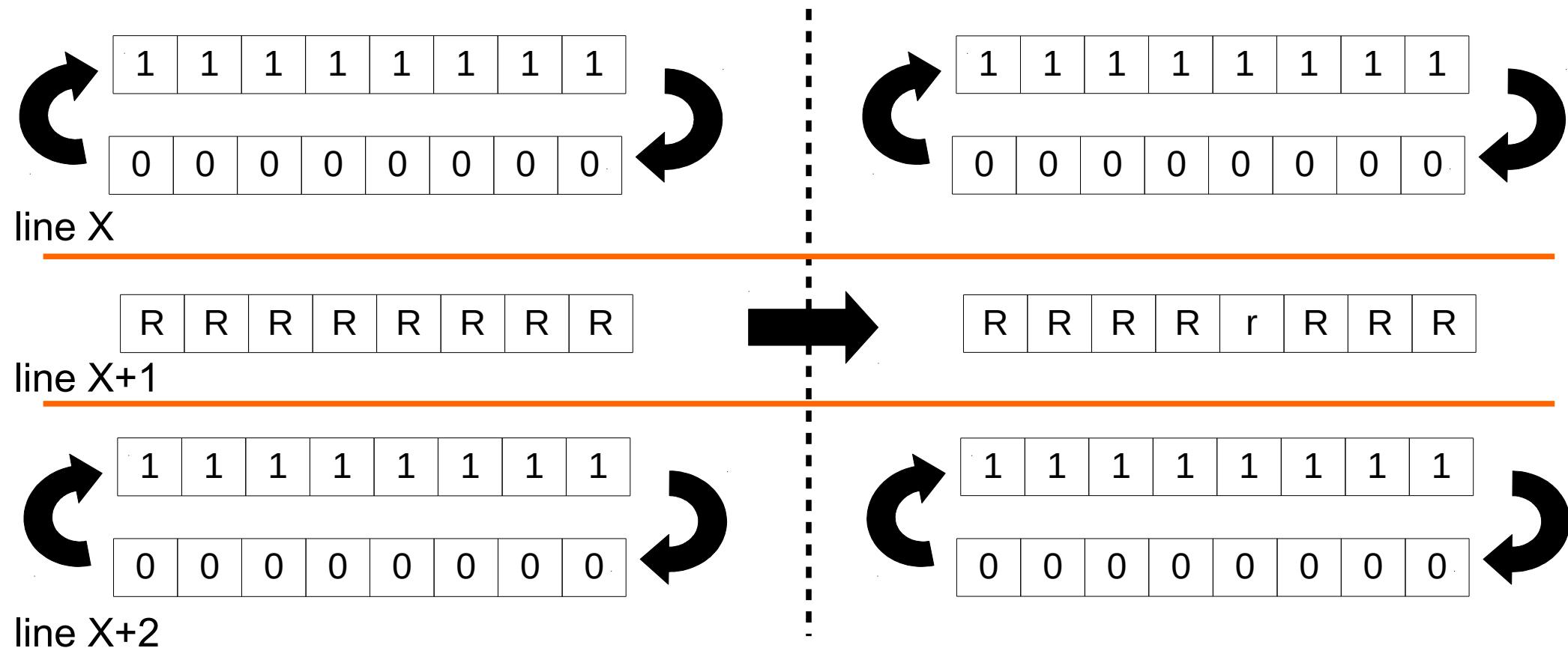

# Manipulation of neighbouring cells

# Implementation and testing of attacks

- The attacks selected are easily implementable

- They do not have extensive requirements

- Are accessible to inexperienced attackers

- They target SRAM PUFs which are already in production

- Can therefore serve to determine if current PUF **products** can actually be considered as an *acceptable* security mechanism

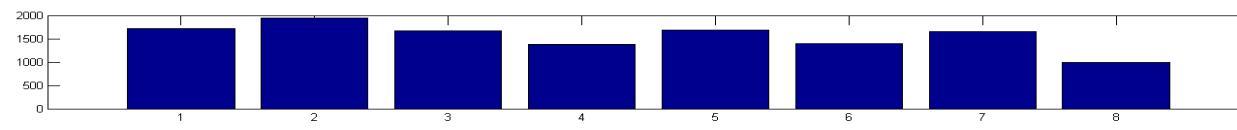

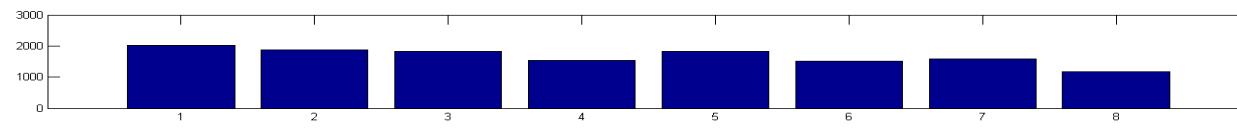

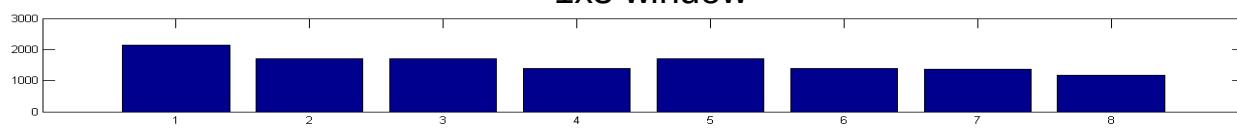

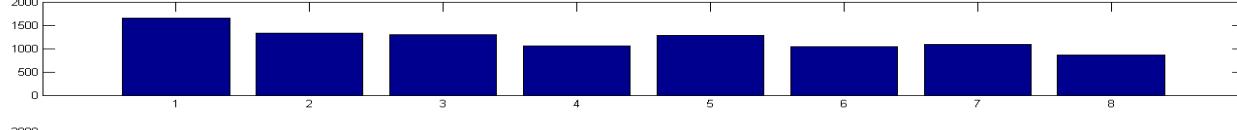

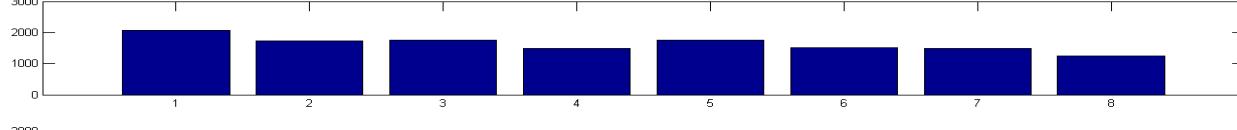

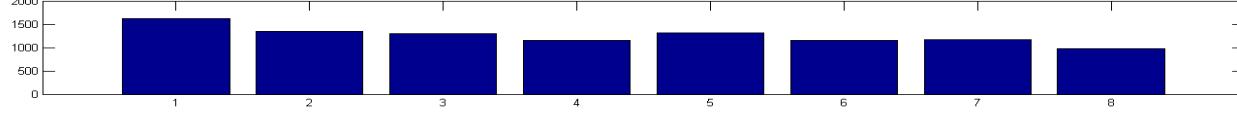

# Metrics to examine dependencies between nearby SRAM cells

## Entropy in SRAM responses

- Has already been investigated for logical layout

- There is a need to prove or disprove if SRAM PUFs can be modelled based on the response of neighbouring cells (+error correction)

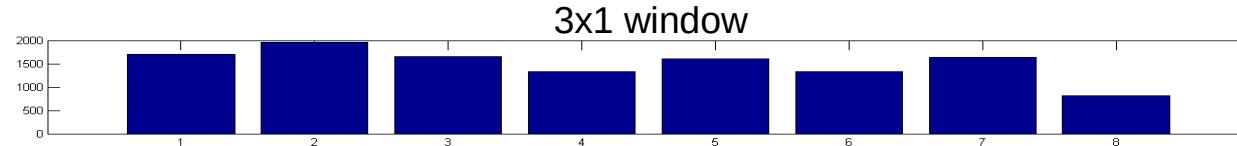

3x1 window

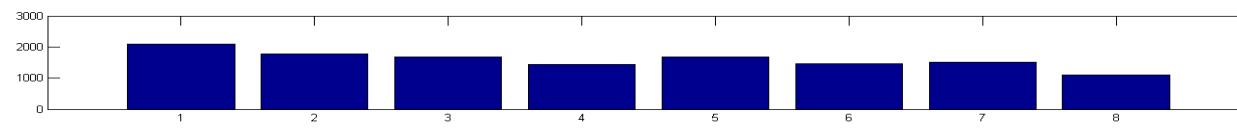

1x3 window

k: known values

- We examine the physical layout

- Estimate the value of a central cell in windows of different sizes, when values of all other cells are known

- Data obtained by TU Berlin

- 2 chips tested

# Metrics to examine dependencies between nearby SRAM cells

Chip 1 physical layout

Chip 1 logical layout

Chip 2 physical layout

Chip 2 logical layout

Chip 1 physical layout

Chip 1 logical layout

Chip 2 physical layout

Chip 2 logical layout

First experiments indicate a good entropy

# Future objectives

- Complete assessment of current PUF solutions regarding their security

- Assess and improve the error correction mechanism

- Identify possible new PUF solutions

- Pick and implement better PUF solutions and protocols

# Future collaborations

- PUF-based attestation (internal)

- Novel PUF solutions (external)

- Side-channel attacks on PUFs (internal & external)

- PUF-based communication protocols (internal & external)

# Future collaborations